Samsung desafia TSMC com chips de 2 nm para 2025

Samsung anuncia chips de 2 nanômetros para 2025, e quer chegar à marca de 1,4 nm em 2027; a meta é bater de frente com TSMC e Apple

Ronaldo Gogoni 43 semanas atrás

A Samsung está investindo pesado no desenvolvimento de novos e melhores processos de litografia para semicondutores. Sua divisão dedicada foi a primeira companhia a produzir chips de 3 nm em massa, em 2022, e quer continuar à frente das rivais, especialmente a TSMC, fornecedora exclusiva da Apple.

Na última terça-feira (27), a divisão de chips da gigante sul-coreana revelou, durante seu fórum anual, os planos para alcançar a marca de 2 nm em 2025, e reduzir ainda mais a litografia, alcançando 1,4 nm em 2027.

Da esq. para a dir.: Jung-Chul Jung, SVP da divisão de chips da Samsung, Koo Ja-hum, VP, e Kang Sang-beom, SVP, exibem wafers de 3 nm quando do início da produção em massa, em foto de 2022 (Crédito: Divulgação/Samsung)

O anúncio foi feito em meio a uma guerra travada entre a Samsung e a TSMC, no que a companhia taiwanesa superou os coreanos, e posteriormente assumiu, sozinha, o posto de fornecedora de chips para os dispositivos da maçã.

Hoje, as linhas AX, AXX e Silicon dão canseira em todos os concorrentes, seja em mobile ou desktop, incluindo Intel e AMD, enquanto a Nvidia, que usou os componentes de 8 nm da Samsung na família de GPUs RTX 30 Series, voltou a trabalhar com a TSMC na série 40 (5 nm), mesmo com maior litografia.

Suas linhas de placas de vídeo para soluções de alto nível, como as poderosas A100, A800, H100 e H800, também são equipadas com semicondutores Made in Taiwan, e mesmo com a Samsung oferecendo uma litografia menor, de 3 nm, A Nvidia não se interessou.

O que aconteceu com a Samsung foi timing e qualidade. Enquanto batia no peito clamando ser pioneira em desenvolvimento de chips com litografias realmente pequenas, o que era verdade, a TSMC eventualmente alcançava a rival, atendendo as requisições dos clientes, como Apple e Nvidia, com melhor desenvoltura.

Embora na percepção geral, iPhones equipados com chips da Samsung não ficavam tão atrás quando comparados aos da TSMC, havia sim uma diferença, o suficiente para a maçã, que queria há tempos uma justificativa para remover a Samsung de sua lista de fornecedores, fechar com a parceira de Taiwan o fornecimento exclusivo.

À Samsung, restou correr atrás do prejuízo, resolvido em tese em 2022. A nova linha de semicondutores não só era a primeira de 3 nm em massa, mas também a primeira a abandonar o tradicional processo FinFET, e adotar o novo Gate-All-Around (GAA).

Vamos recapitular: quanto mais os fabricantes reduziam o tamanho de seus transístores, mais próximos eles ficavam uns dos outros, o que poderia ocasionar saltos de energia involuntários entre os terminais, o que tornaria a redução da litografia inviável em certo ponto.

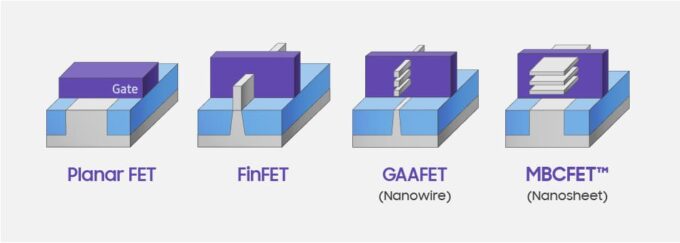

A Intel notou o problema na migração dos 30 nm para 20 nm, e a solução encontrada foi fazer a porta (gate) se sobrepor ao canal, que comporta a fonte (source) e o dreno (sink). O processo FinFET se traduz como "transístor de efeito de campo em nadadeira", devido o formato da barreira, com as pontas expostas.

A Intel adotou o processo FinFET (ou Tri-Gate, como ela o chamava) na linha de processadores Ivy Bridge, de 22 nm, lançada em 2012, mas se sabia na época que o design não iria durar, quanto mais os transístores encolhiam, e o problema voltou quando a marca de 5 nm foi alcançada.

A Samsung considerou que para chegar aos 3 nm, era preciso usar um novo arranjo, e é aí que entra o Gate-All-Around, ou GAA.

Comparação entre os arranjos planar (2D), FinFEt, e os dois modelos de GAA (Crédito: Divulgação/Samsung)

No FinFET, a porta está sobreposta ao canal, enquanto no GAA ela o envolve totalmente, estes sendo nanotubos (GAAFET), ou nanofolhas (MBCFET). Tal design reduz novamente os problemas de flutuação energética, e viabiliza uma maior miniaturização dos componentes.

A Samsung migrou para o GAAFET em 2022, com seu design de 3 nm, e agora pretende pular para o MBCFET em 2025, no que pretende, mais uma vez, tomar a dianteira do setor, chegando aos 2 nanômetros antes da TSMC.

A ideia é oferecer chips mais rápidos e eficientes a clientes de peso, como IBM, Nvidia, Qualcomm e Baidu, entre outros clientes da adversária de Taiwan que não a Apple, que claro, nunca mais voltará a comprar nada dos coreanos, com exceção de telas, e mesmo isso não deve durar muito mais.

Já a TSMC entrou nos 3 nm no fim de 2022, no que a maçã comprou o lote inteiro, mas seu design é uma versão customizada do FinFET, chamado FinFlex; a companhia pretende pular para o GAA apenas com os 2 nm, também em 2025.

Ao mesmo tempo, a Samsung anunciou que até 2027, deverá aprimorar o processo de impressão de 2 nm para lançar os primeiros chips com litografia de 1,4 nm.

Agora, a Samsung precisa convencer os clientes a comprarem na sua mão, de preferência, com prioridade.

Mesmo com um design supostamente superior nos 3 nm (GAAFET vs. FinFlex), a Nvidia, que é uma companhia fabless (não imprime os chips que desenvolve), fechou exclusividade com a TSMC, alegando uma menor demanda não exige dois fornecedores.

Já AMD e Qualcomm compraram com as duas companhias, mas deram prioridade aos taiwaneses.

Fonte: Extreme Tech, AnandTech